A standard 24-transistor implementation of a static 1-bit full

4.9 (705) · $ 18.50 · In stock

Compact implementation of F05: (A ⊕ B) · C. Any combination of

CMOS full adder cells based on modified full swing restored complementary pass transistor logic for energy efficient high speed arithmetic applications - ScienceDirect

Fast and High-Performing 1-Bit Full Adder Circuit Based on Input Switching Activity Patterns and Gate Diffusion Input Technique

Design and analysis of hybrid 10T adder for low power applications - ScienceDirect

Design a novel 1-bit full adder with hybrid logic for full-swing, area-efficiency and high-speed

A standard 24-transistor implementation of a static 1-bit full adder

A standard 24-transistor implementation of a static 1-bit full adder

Design of Low-Power 10-Transistor Full Adder Using GDI Technique for Energy-Efficient Arithmetic Applications

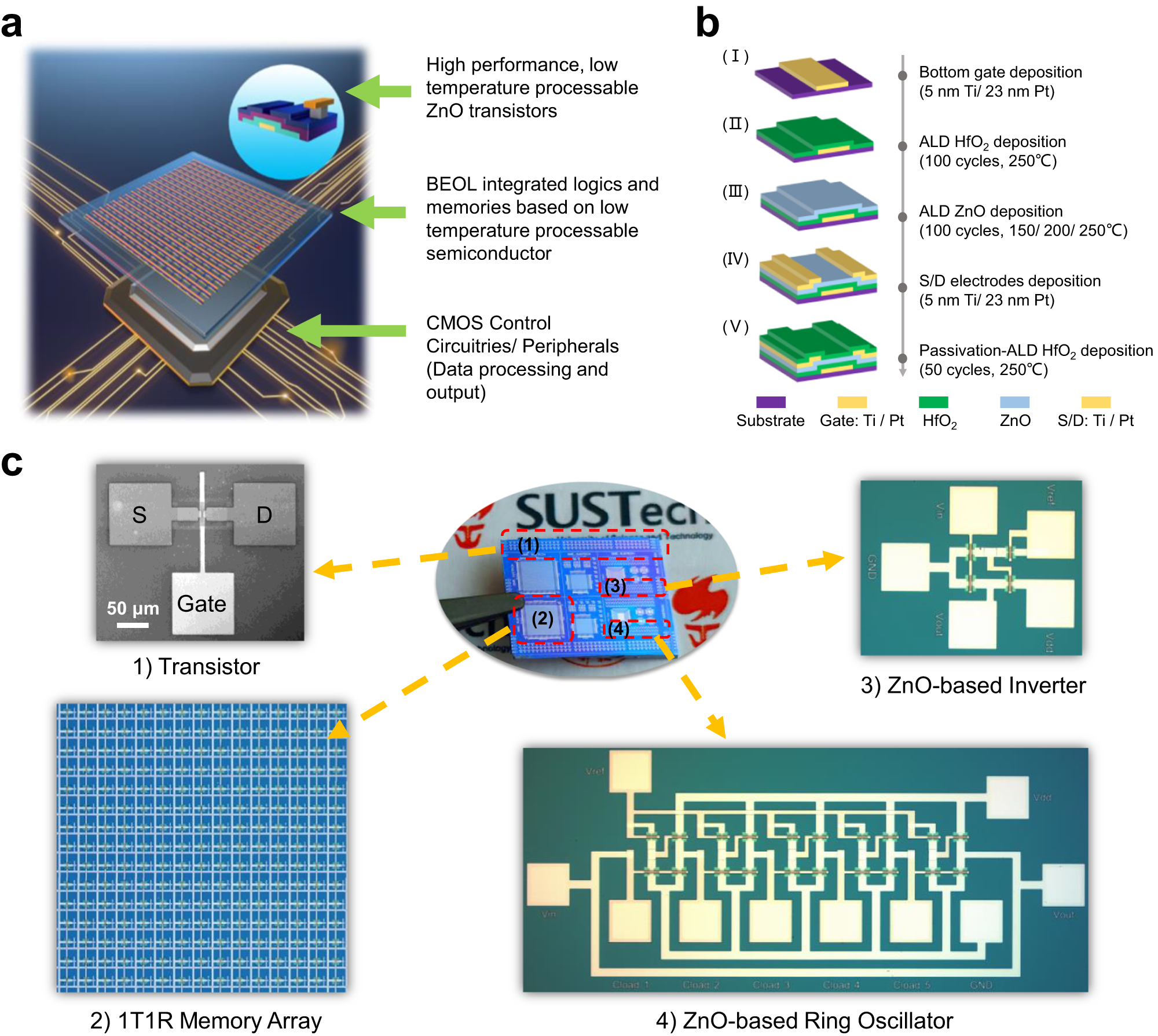

CMOS backend-of-line compatible memory array and logic circuitries enabled by high performance atomic layer deposited ZnO thin-film transistor

Fast and energy efficient full adder circuit using 14 CNFETs - ScienceDirect

Implementing a 1-bit full adder using GDI technique

Karnaugh maps for Boolean function F1 and corresponding standard

![Mirror full adder schematic [4]](https://www.researchgate.net/profile/Vazgen-Melikyan-2/publication/224596966/figure/fig1/AS:302682326749184@1449176498259/Mirror-full-adder-schematic-4_Q320.jpg)

Mirror full adder schematic [4]

How to realize F=(AB+ACE+CD+DBE)' using CMOS with the minimum number of transistors - Quora